# ES1946 Solo-1E™ PCI AudioDrive® Notebook Solution Data Sheet

# DESCRIPTION

The ES1946 Solo-1E™ PCI AudioDrive® solution implements a single-chip PCI audio solution, providing high-quality audio processing while maintaining full legacy DOS game compatibility. With a dynamic range over 80 dB, the ES1946 complies with the Microsoft® PC 97 / PC 98 / PC 99 specifications and meets WHQL audio requirements. The ES1946 forms a complete audio subsystem on a single chip for notebook platforms.

The ES1946 includes an I<sup>2</sup>S Zoom Video port interface which allows playback of MPEG audio using the 16-bit stereo music DAC; thus reducing the total audio solution chip count.

The ES1946 incorporates a microcontroller, ESFM™ music synthesizer, 16-bit stereo wave ADC and DAC, 16-bit stereo music DAC, MPU-401 UART mode serial port, I²S Zoom Video port, serial port interface to external wavetable music synthesizer, dual game port, hardware master volume control, DMA control logic with FIFO, and PCI bus interface logic. There are three stereo inputs (typically line-in, CD audio, and auxiliary line) and a mono microphone input.

The ES1946 also incorporates **Spatializer®** VBX<sup>™</sup> technology, provided by Desper Products, Inc., a subsidiary of Spatializer Audio Laboratories, Inc. This processor expands the stereo sound field emitted by two speakers to create a resonant 3-D sound environment.

The ES1946 integrates ESS' field-proven hardware design for DOS game compatibility with hardware FM synthesis (ESFM™ synthesis) and three methods for legacy audio control interface: PC/PCI, Distributed DMA, and Transparent DMA. Transparent DMA requires no sideband signals from PC core logic chipsets in addition to the standard PCI 2.2 bus. TDMA is compatible with Pentium®, Pentium II®, and Pentium Pro® chipsets as well as standard PCI add-in cards.

The ES1946 provides a serial EEPROM interface for ease of programming the Subsystem ID and Subsystem Vendor ID.

The ES1946 can record, compress, and play back voice, sound, and music with built-in mixer controls. It supports stereo full-duplex operation for simultaneous record and playback. The ESFM™ synthesizer has extended capabilities within native mode operation providing superior sound and power-down capabilities.

The ES1946 is compliant with Advanced Power Management (APM) 1.2, Advanced Configuration and Power Interface (ACPI) 1.0, and PCI Power Management Interface (PPMI) 1.0.

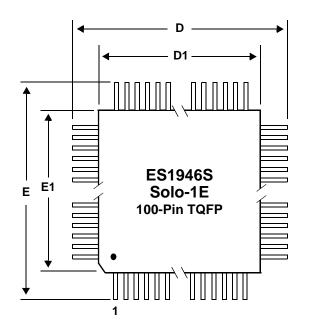

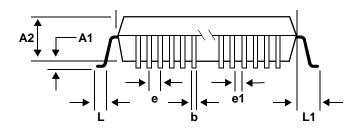

It is available in an industry-standard 100-pin Thin Quad Flat Pack (TQFP) package.

# **FEATURES**

- Single, high-performance, mixed-signal, 16-bit stereo VLSI chip

- PCI parallel bus interface, revision 2.2

- Full native DOS games compatibility, via three technologies:

- TDMA

- DDMA

- PC/PCI

- High-quality ESFM™ music synthesizer

- Dynamic range (SNR) over 80 dB

- · Serial EEPROM interface for SID and SVID resource

- Integrated

Spatializer® 3-D VBX™ stereo audio effects

technology provided by Desper Products, Inc., a subsidiary of

Spatializer Audio Laboratories, Inc.

# **Record and Playback Features**

- Record, compress, and play back voice, sound, and music

- 16-bit stereo ADC and DAC

- Programmable independent sample rates from 6 kHz up to 48 kHz for record and playback

- Full-duplex operation for simultaneous record and playback

- 2-wire hardware volume control for up, down, and mute

# Inputs and Outputs

- Stereo inputs for line-in, auxiliary A (CD audio), and auxiliary B, and a mono input for microphone

- I<sup>2</sup>S Zoom Video port interface for MPEG audio at up to 48 kHz

- MPU-401 (UART mode) interface for wavetable synthesizers and MIDI devices

- Integrated dual game port

- Separate mono input (MONO\_IN) and mono output (MONO\_OUT) for speakerphone

# **Mixer Features**

- 7-channel mixer with stereo inputs for line, CD audio, auxiliary line, music synthesizer, digital audio (wave files), and mono inputs for microphone and speakerphone

- Programmable 6-bit logarithmic master volume control

# Power

Advanced power management meets APM 1.2, ACPI 1.0, and PPMI 1.0 standards

# Compatibility

- Supports PC games and applications for Sound Blaster™ and Sound Blaster™ Pro

- Supports Microsoft® Windows™ Sound System®

- Meets PC 97 / PC 98 / PC 99 and WHQL specifications

2

<sup>\* 3-</sup>D Processor uses

Spatializer VBXTM 3-D technology provided by Desper Products, Inc. a subsidiary of Spatializer Audio Laboratories, Inc.

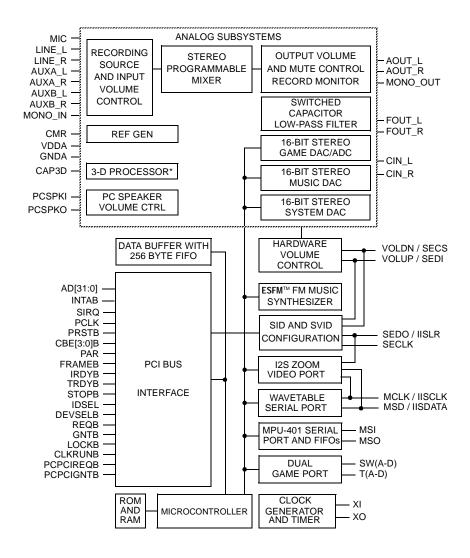

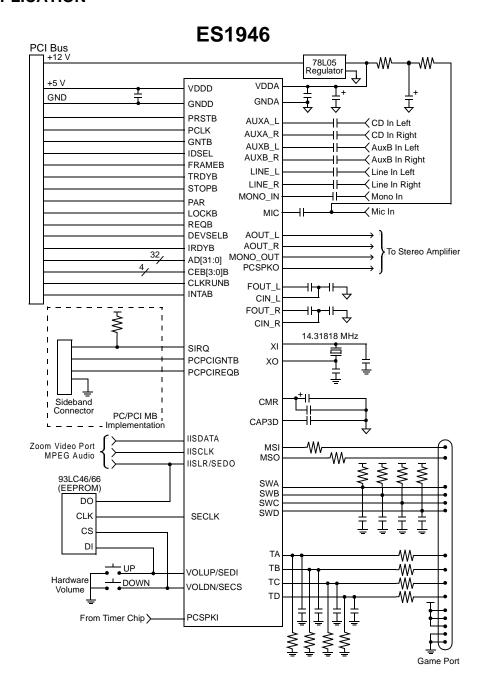

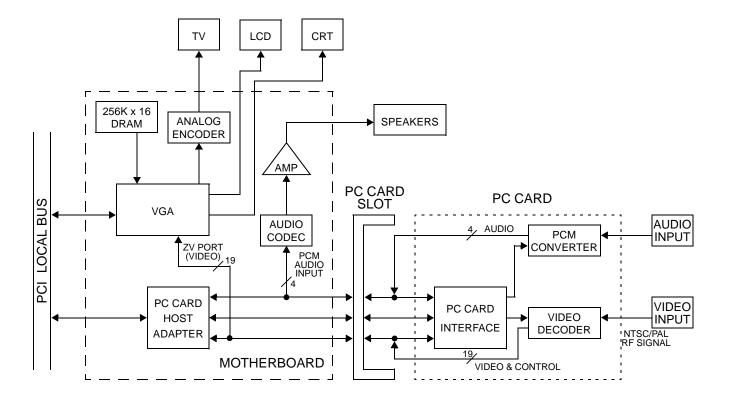

Figure 1 Block Diagram

# CONTENTS

# **CONTENTS**

| DESCRIPTION 1                                              | Programming for DOS Game Compatibility 24           |

|------------------------------------------------------------|-----------------------------------------------------|

| FEATURES                                                   | Selecting DMA/IRQ Policy                            |

| CONTENTS 3                                                 | Programming for Native PCI Audio                    |

| FIGURES 4                                                  | Modes of Operation                                  |

| TABLES 4                                                   | Data Formats                                        |

| PINOUT 5                                                   | Compatibility Mode Programming27                    |

| PIN DESCRIPTION 6                                          | Extended Mode Programming29                         |

| FUNCTIONAL DESCRIPTION                                     | Programming the ES1946 Mixer35                      |

| Digital Subsystems9                                        | PROGRAMMING MODEL                                   |

| Analog Subsystems                                          | Register Types                                      |

| MIXER SCHEMATIC BLOCK DIAGRAM                              | PCI Configuration Registers                         |

| TYPICAL APPLICATION                                        | I/O Ports                                           |

| BUS INTERFACING                                            | Port Summary                                        |

| DIGITAL AUDIO                                              | Port Descriptions                                   |

| DMA Simulation Modes                                       | Mixer Registers54                                   |

| Audio Channels                                             | AUDIO MICROCONTROLLER COMMAND SUMMARY67             |

| Data Formats                                               | POWER MANAGEMENT                                    |

| Audio 1 DMA Transfers in legacy DOS Compatibility Mode .13 | CLKRUN Protocol                                     |

| Audio 1 DMA Transfers in Extended Mode                     | PCI Power Management Interface (PPMI) 69            |

| Audio 1 DMA Transfers in Native PCI Mode                   | ELECTRICAL CHARACTERISTICS70                        |

| Data Transfers Using the Second Audio Channel 14           | Absolute Maximum Ratings                            |

| First DMA Channel CODEC                                    | Thermal Characteristics                             |

| NTERRUPTS                                                  | Operating Conditions                                |

| Interrupt Status Register                                  | Operating Current (Typical)                         |

| Interrupt Mask Register                                    | TIMING DIAGRAMS72                                   |

| PERIPHERAL INTERFACING                                     | TIMING CHARACTERISTICS74                            |

| I <sup>2</sup> S Serial Interface                          | MECHANICAL DIMENSIONS75                             |

| Wavetable Interface                                        | APPENDIX A: ES689/ES69X DIGITAL SERIAL INTERFACE 76 |

| Joystick / MPU-401 Interface                               | APPENDIX B: I'S ZV INTERFACE REFERENCE77            |

| MONO_IN and MONO_OUT                                       | Overview77                                          |

| Spatializer® VBX™ Audio Processor 19                       | The Audio Interface78                               |

| Hardware and Master Volume Control                         | Audio Interface Timing                              |

| PC Speaker                                                 | LRCLK79                                             |

| Serial EEPROM Interface                                    | SCLK79                                              |

| ANALOG DESIGN CONSIDERATIONS                               | SDATA79                                             |

| MONO_IN and MONO_OUT                                       | MCLK79                                              |

| Reference Generator                                        | ZV Port Pin Assignments                             |

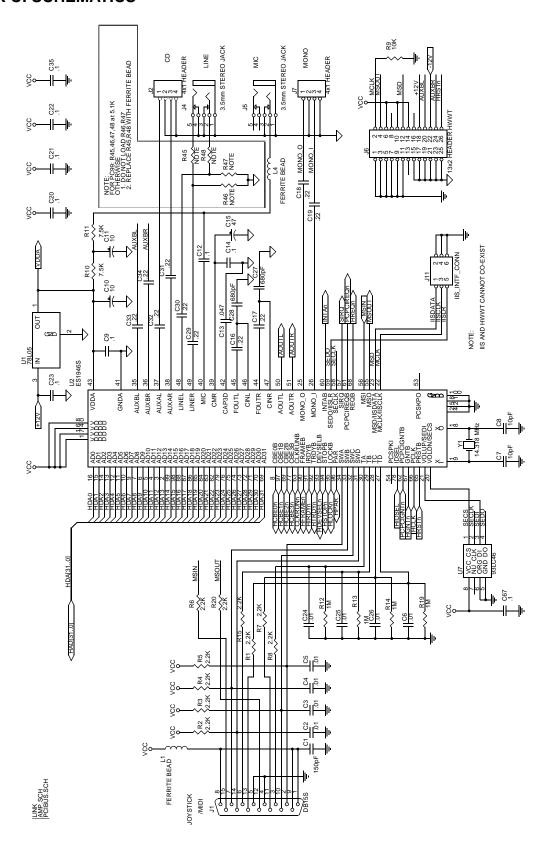

| Switched-Capacitor Filter                                  | APPENDIX C: SCHEMATICS82                            |

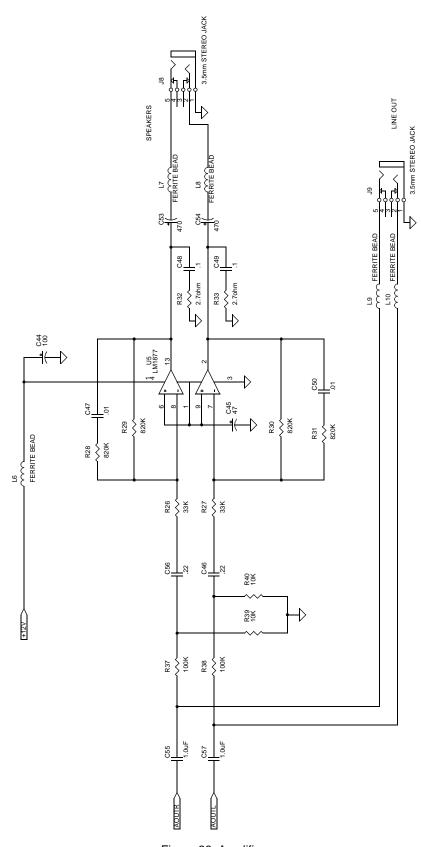

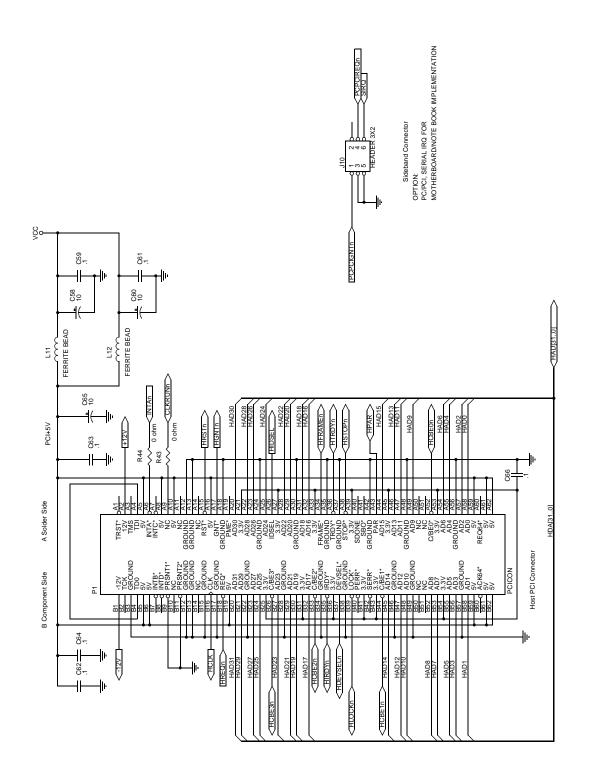

| Audio Inputs and Outputs                                   | APPENDIX D: BILL OF MATERIALS85                     |

| PROGRAMMING THE ES1946                                     | APPENDIX E: LAYOUT GUIDELINES                       |

| Identifying the ES1946                                     | PCB Layout86                                        |

| Resetting and Initializing the ES1946                      | •                                                   |

|                                                            |                                                     |

# **FIGURES**

| Figure 1 Block Diagram                                                                                                                                                                                                                                                                          | Figure 16 PRST Timing                                                              | 72<br>73<br>73<br>75<br>77<br>78 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|----------------------------------|

| Figure 9 PC Speaker Volume Circuitry 20 Figure 10 Serial EEPROM – Typical Application 20 Figure 11 Analog Ground Plane Diagram 22 Figure 12 Reference Generator Pin Diagram 22 Figure 13 Switched-Capacitor Filter Pin Diagram 22 Figure 14 Command Transfer Timing 27 Figure 15 PCLK Timing 72 | Figure 24 I2S Digital Input Format with 16 SCLK periods Figure 25 ES1946 Schematic | 80<br>82<br>83<br>84<br>86       |

| TABLES                                                                                                                                                                                                                                                                                          |                                                                                    |                                  |

| Table 1 PCI Bus Interface Pins       12         Table 2 Extended Mode Audio 1 Controller Registers       14         Table 3 Audio 2 Related Mixer Registers       15         Table 4 ES1946 Interrupt Sources       16         Table 5 Interrupt Status Rite in IORace Th       16              | Table 21 Mixer Input Volume Registers                                              | 39<br>43<br>46                   |

| Table 1  | PCI Bus Interface Pins                         | Table 21 | Mixer Input Volume Registers              | 7 |

|----------|------------------------------------------------|----------|-------------------------------------------|---|

| Table 2  | Extended Mode Audio 1 Controller Registers14   | Table 22 | PCI Configuration Registers Summary 39    | ) |

| Table 3  | Audio 2 Related Mixer Registers15              | Table 23 | Supported Legacy Audio Addresses 43       | 3 |

| Table 4  | ES1946 Interrupt Sources16                     | Table 24 | I/O Port Base Addresses                   | 3 |

| Table 5  | Interrupt Status Bits in IOBase+7h16           | Table 25 | I/O Port Summary                          | 3 |

| Table 6  | I2S Interface Pins                             |          | EEPROM Auto-detect ID Bytes 48            |   |

| Table 7  | Wavetable Interface Pins17                     | Table 27 | EEPROM Access Command Summary 48          | 3 |

| Table 8  | Hardware and Software Reset Initializations23  | Table 28 | Sound Blaster Support Register Summary 54 | 4 |

| Table 9  | ISA DMA Policy Bits for Add-On Cards24         | Table 29 | ESS Mixer Registers Summary 54            | 1 |

| Table 10 | ISA DMA Policy Bits for Motherboards 24        | Table 30 | Mixer Register Default Values 56          | 3 |

| Table 11 | ISA IRQ Emulation Policy Bits24                | Table 31 | Music DAC Source 61                       | 1 |

| Table 12 | Comparison of Operation Modes26                | Table 32 | ESS Controller Registers Summary 62       | 2 |

| Table 13 | Uncompressed DAC Transfer Modes                | Table 33 | Command Summary 67                        | 7 |

| Table 14 | Uncompressed ADC Transfer Modes                | Table 34 | Digital Characteristics 70                | ) |

| Table 15 | Command Sequences for DMA Playback31           | Table 35 | Analog Characteristics                    | 1 |

| Table 16 | Command Sequence for DMA Record                | Table 36 | Timing Characteristics                    | 1 |

| Table 17 | Sound Blaster Pro/Extended Access Registers 35 | Table 37 | Common Clock Frequencies                  | 3 |

| Table 18 | SB Pro Read Volume Emulation                   | Table 38 | AC Parameters for Audio Signals 79        | Э |

| Table 19 | SB Pro Write Volume Emulation                  | Table 39 | ZV Port Interface Pin Assignments 81      | 1 |

| Table 20 | Extended Access Mixer Volume Values 37         | Table 40 | FS1946 Bill of Materials (BOM) 85         | 5 |

ESS Technology, Inc. SAM0219-051998

5

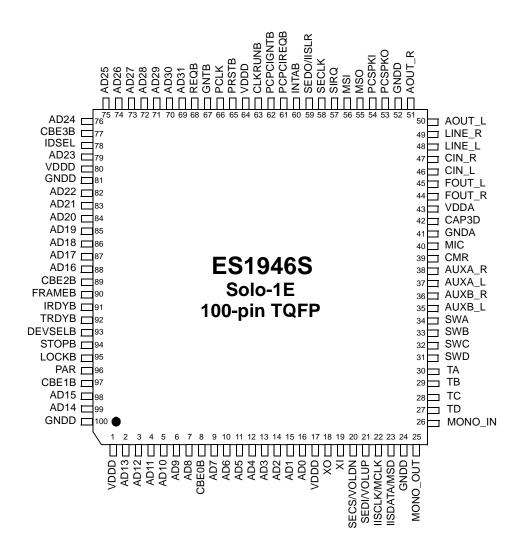

# **PINOUT**

Figure 2 ES1946 Pinout

# **PIN DESCRIPTION**

| Name      | Number                                | I/O | Description                                                                                                                                                 |

|-----------|---------------------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDDD      | 1,17,64,80                            | ı   | Digital supply voltage (5 V ± 5%).                                                                                                                          |

| AD[31:0]  | 69–76,79,<br>82–88,98,99,<br>2–7,9–16 | I/O | Address and data lines from the PCI bus.                                                                                                                    |

| CBE[3:0]B | 77,89,97,8                            | I/O | PCI command/byte enable.                                                                                                                                    |

| XO        | 18                                    | 0   | Oscillator output. Connect to external 14.318 MHz crystal.                                                                                                  |

| ΧI        | 19                                    | I   | Oscillator/external clock input. Connect to external 14.318 MHz crystal or clock source (must be CMOS levels).                                              |

| VOLDN     | 20                                    | I   | Active-low volume decrease button input with internal pull-up.                                                                                              |

| SECS      | 20                                    | 0   | Serial EEPROM chip select.                                                                                                                                  |

| VOLUP     | 04                                    | I   | Active-low volume increase button input with internal pull-up.                                                                                              |

| SEDI      | 21                                    | 0   | Serial data output to EEPROM.                                                                                                                               |

| MCLK      | 22                                    | I   | Input with internal pull-down. Music serial clock from external wavetable music synthesizer (ES692).                                                        |

| IISCLK    |                                       | I   | Serial shift clock for I <sup>2</sup> S interface.                                                                                                          |

| MSD       | 23                                    | -   | Input with internal pull-down. Music serial data from external wavetable music synthesizer (ES692).                                                         |

| IISDATA   |                                       | I   | Serial data for I <sup>2</sup> S interface.                                                                                                                 |

| GNDD      | 24,52,81,100                          | I   | Digital ground.                                                                                                                                             |

| MONO_OUT  | 25                                    | 0   | Mono output with source select and volume control (including mute). This pin can drive an external 5k $\Omega$ AC load.                                     |

| MONO_IN   | 26                                    | I   | Mono input to mixer and ADC. This pin has an internal pull-up to CMR.                                                                                       |

| T(A-D)    | 30:27                                 | I/O | Joystick timer pins. These pins connect to the X-Y positioning variable resistors for the two joysticks.                                                    |

| SW(A-D)   | 34:31                                 | I   | Active-low joystick switch setting inputs. These SW pins have internal pull-up resistors.                                                                   |

| AUXB_L    | 35                                    | I   | Auxiliary B input, left. AUXB_L has an internal pull-up resistor to CMR.                                                                                    |

| AUXB_R    | 36                                    | I   | Auxiliary B input, right. AUXB_R has an internal pull-up resistor to CMR.                                                                                   |

| AUXA_L    | 37                                    | I   | Auxiliary A input, left. AUXA_L has an internal pull-up resistor to CMR. Normally intended for connection to an internal or external CD-ROM analog output.  |

| AUXA_R    | 38                                    | I   | Auxiliary A input, right. AUXA_R has an internal pull-up resistor to CMR. Normally intended for connection to an internal or external CD-ROM analog output. |

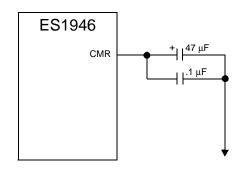

| CMR       | 39                                    | 0   | Common mode reference voltage (2.25 V $\pm$ 5%). Bypass this pin to analog ground with 47 $\mu$ F electrolytic in parallel with a .1 $\mu$ F capacitor.     |

| MIC       | 40                                    | I   | Microphone input. MIC has an internal pull-up resistor to CMR.                                                                                              |

| GNDA      | 41                                    | I   | Analog ground.                                                                                                                                              |

| CAP3D     | 42                                    | I   | Bypass capacitor to analog ground for 3-D effects.                                                                                                          |

| VDDA      | 43                                    | I   | Analog supply voltage (5 V $\pm$ 5%). Must be greater than or equal to VDDD - 0.3 V.                                                                        |

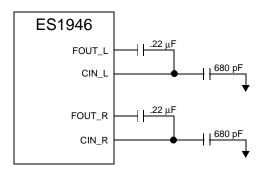

| FOUT_R,   | 44                                    | 0   | Filter output, right. AC-coupled externally to CIN_R to remove DC offsets.                                                                                  |

| FOUT_L    | 45                                    | 0   | Filter output, left. AC-coupled externally to CIN_L to remove DC offsets.                                                                                   |

| CIN_L     | 46                                    | I   | ADC and first channel DAC mixer input. This pin has an internal 50k $\Omega$ pull-up resistor to CMR.                                                       |

| CIN_R     | 47                                    | I   | ADC and first channel DAC mixer input. This pin has an internal 50k $\Omega$ pull-up resistor to CMR.                                                       |

| LINE_L    | 48                                    | I   | Line input, left. LINE_L has an internal pull-up resistor to CMR.                                                                                           |

| LINE_R    | 49                                    | -1  | Line input, right. LINE_R has an internal pull-up resistor to CMR.                                                                                          |

| AOUT_L    | 50                                    | 0   | Line-level stereo output, left. This pin can drive a 5k $\Omega$ AC load.                                                                                   |

# PIN DESCRIPTION

| Name      | Number | I/O | Description                                                                                                                                         |

|-----------|--------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| AOUT_R    | 51     | 0   | Line-level stereo output, right. This pin can drive a 5k $\Omega$ AC load.                                                                          |

| PCSPKO    | 53     | 0   | Analog output of PCSPKI with volume control.                                                                                                        |

| PCSPKI    | 54     | ı   | Normally low digital PC speaker signal input. This signal is converted to an analog signal with volume control and appears on analog output PCSPKO. |

| MSO       | 55     | 0   | MIDI serial data output.                                                                                                                            |

| MSI       | 56     | I   | MIDI serial input. Schmitt trigger input with internal pull-up resistor. Either MPU-401 or Sound Blaster formats.                                   |

| SIRQ      | 57     | I/O | Serialized IRQ. (Optional motherboard PC/PCI implementation.)                                                                                       |

| SECLK     | 58     | 0   | Clock for serial EEPROM.                                                                                                                            |

| SEDO      | 59     | I   | Serial data input from EEPROM.                                                                                                                      |

| IISLR     | 59     | I   | Left/Right strobe for I2S interface.                                                                                                                |

| INTAB     | 60     | 0   | PCI interrupt request.                                                                                                                              |

| PCPCIREQB | 61     | 0   | PC/PCI serialized DREQ output. (Optional motherboard PC/PCI implementation.)                                                                        |

| PCPCIGNTB | 62     | I   | PC/PCI serialized DACK input. (Optional motherboard PC/PCI implementation.)                                                                         |

| CLKRUNB   | 63     | I/O | PCI clock state for power management.                                                                                                               |

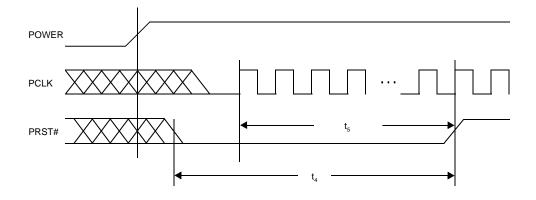

| PRSTB     | 65     | I   | PCI reset.                                                                                                                                          |

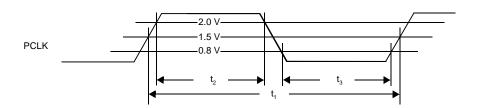

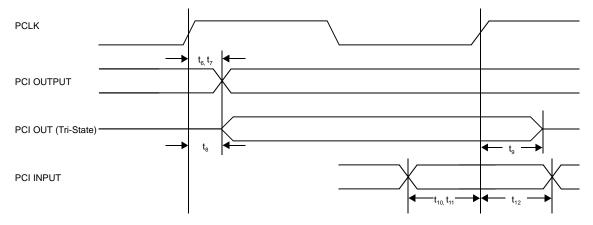

| PCLK      | 66     | I   | PCI clock. This clock times all PCI transactions.                                                                                                   |

| GNTB      | 67     | I   | PCI busmaster grant.                                                                                                                                |

| REQB      | 68     | 0   | PCI busmaster request, tri-state output.                                                                                                            |

| IDSEL     | 78     | I   | PCI device select for configuration.                                                                                                                |

| FRAMEB    | 90     | I/O | PCI cycle frame.                                                                                                                                    |

| IRDYB     | 91     | I/O | PCI initiator ready.                                                                                                                                |

| TRDYB     | 92     | I/O | PCI target ready.                                                                                                                                   |

| DEVSELB   | 93     | I/O | PCI device select.                                                                                                                                  |

| STOPB     | 94     | I/O | PCI stop transaction.                                                                                                                               |

| LOCKB     | 95     | I/O | PCI lock.                                                                                                                                           |

| PAR       | 96     | I/O | PCI parity.                                                                                                                                         |

# **FUNCTIONAL DESCRIPTION**

This section shows the overall structure of the ES1946 and discusses its major functional subunits.

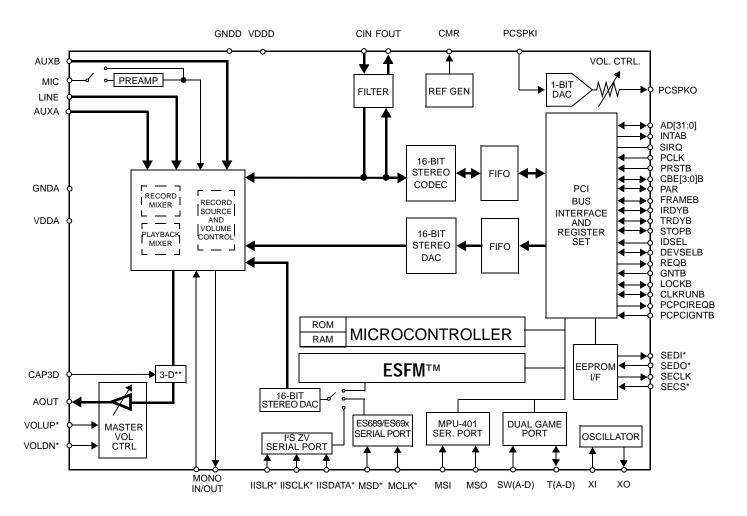

The major subunits of the ES1946 are shown in Figure 3 and described briefly in the following paragraphs.

<sup>\*</sup> Some of these pins are shared with other functions.

Figure 3 ES1946 Block Diagram

<sup>\*\* 3-</sup>D Processor uses **Spatializer** ° VBX™ 3-D technology provided by Desper Products, Inc., a subsidiary of Spatializer Audio Laboratories, Inc.

# **Digital Subsystems**

- RISC microcontroller game-compatible audio functions are performed by an embedded microcontroller.

- ROM and RAM firmware ROM and data RAM to the embedded microcontroller.

- Oscillator circuitry to support an external crystal.

- FIFO RAM for a 256-byte FIFO data buffer for use with the first audio channel and RAM for a 64-byte FIFO data buffer for use with the second audio channel.

- PCI bus interface provides interface to PCI bus signals. The PCI 2.2 compliant interface supports bus master/slave.

- Dual game port integrated dual game port for two joysticks.

- MPU-401 serial port asynchronous serial port for MIDI devices such as a wavetable synthesizer or a music keyboard input.

- EEPROM interface serial port connection from a 93LC66/46 EEPROM providing Subsystem ID and Subsystem Vendor ID.

- ESFM™ music synthesizer high-quality, OPL3 superset FM synthesizer with 20 voices.

- Hardware volume control 2 pushbutton inputs with internal pull-up devices for up/down/mute that can be used to adjust the master volume control.

The mute input is defined as the state when both up and down inputs are low simultaneously.

# Analog Subsystems

- Record and Playback Mixers seven input stereo mixers. Each input has independent left and right 4-bit volume control:

- Line In

- Mic In

- Aux A (CD-audio)

- Aux B

- Digitized audio (wave files)

- I2S/FM/ES689/ES69x music DAC

- MONO\_IN/MONO\_OUT

- 16-Bit stereo CODEC for audio record and playback of the first audio channel.

- 16-Bit stereo system DAC for audio playback of the second audio channel.

- 16-Bit stereo music DAC for ESFM<sup>™</sup>, external wavetable synthesizer, or I<sup>2</sup>S Zoom Video port.

- 1-Bit DAC for PC speaker digital input.

- I<sup>2</sup>S Zoom Video serial port supports sample rates up to 48 kHz for MPEG audio.

- Wavetable serial port serial port connection from the output of an ES689 or ES69x that eliminates the need for an external DAC.

- Record source and input volume control input source and volume control for recording. The recording source can be selected from one of four choices:

- Line In

- Mic In

- Aux A (CD-audio)

- Record Mixer

- Output volume and mute control The master volume is controlled either by programmed I/O or by volume control switch inputs. The master volume supports 6 bits per channel.

- Reference generator analog reference voltage generator.

- PC speaker volume control The PC speaker is supported with a 1-bit DAC with volume control. The analog output pin PCSPKO is intended to be externally mixed at the external amplifier.

- · Filter switched capacitor low-pass filter.

- **Pre-amp** 26 dB microphone pre-amplifier.

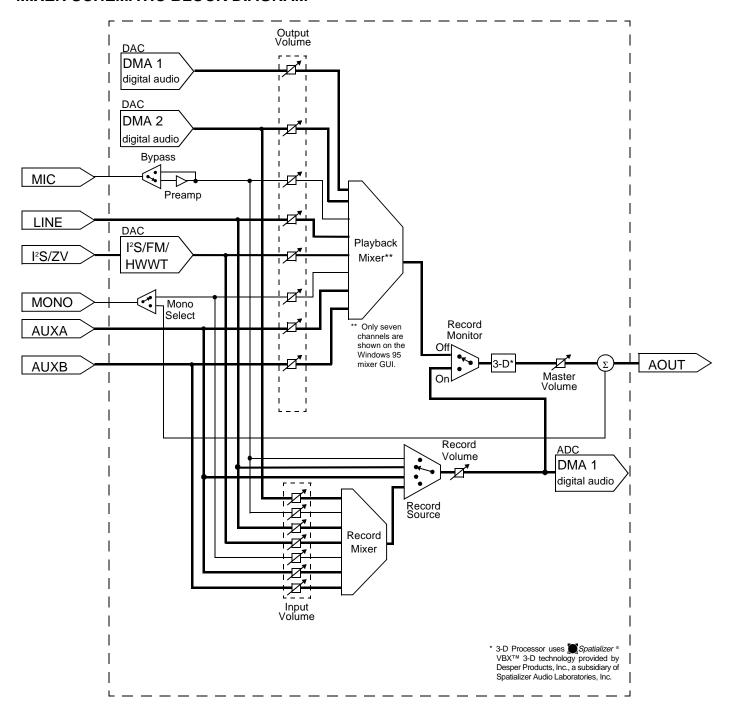

# MIXER SCHEMATIC BLOCK DIAGRAM

Figure 4 ES1946 Mixer Schematic Block Diagram

# TYPICAL APPLICATION

# **BUS INTERFACING**

The ES1946 is compliant with PCI parallel bus interface, version 2.2. This section discusses interfacing to the PC bus, and items relating to configuration for the bus.

Table 1 shows the pins used to interface the ES1946 to the PCI bus.

Table 1 PCI Bus Interface Pins

| Pins      | Descriptions                                                |

|-----------|-------------------------------------------------------------|

| AD[31:0]  | Address and data lines from the PCI bus.                    |

| CBE[3:0]B | PCI command/byte enable.                                    |

| CLKRUNB   | PCI clock state for power management. (optional).           |

| DEVSELB   | PCI device select.                                          |

| FRAMEB    | PCI cycle frame.                                            |

| GNTB      | PCI busmaster grant.                                        |

| IDSEL     | PCI device select for configuration.                        |

| INTAB     | PCI interrupt request.                                      |

| IRDYB     | PCI initiator ready.                                        |

| LOCKB     | PCI lock.                                                   |

| PAR       | PCI parity.                                                 |

| PCLK      | PCI clock. This clock times all PCI transactions.           |

| PCPCIGNTB | PC/PCI serialized DACK input. (Motherboard implementation). |

| PCPCIREQB | PC/PCI serialized DREQ output (Motherboard implementation). |

| PRSTB     | PCI reset.                                                  |

| REQB      | PCI busmaster request, tri-state output.                    |

| STOPB     | PCI stop transaction.                                       |

| TRDYB     | PCI target ready.                                           |

# **DIGITAL AUDIO**

#### **DMA Simulation Modes**

Native PCI mode or PCI Bus Master DMA is used to simulate DMA when the ES1946 is configured as a native PCI device under Windows. See "Programming for Native PCI Audio" on page 25 for more information.

Legacy mode is used for native DOS or DOS box applications. The ES1946 uses TDMA, DDMA, or PCPCI to simulate DMA. See "Programming for DOS Game Compatibility" on page 24 for more information. Once the ES1946 is programmed, the Legacy mode used is transparent to an application using DMA.

# **Audio Channels**

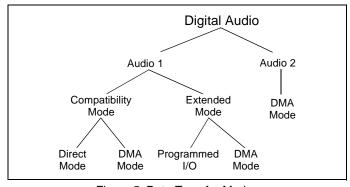

The ES1946 incorporates two digital audio channels.

Audio 1 The first audio channel. This channel is used for Sound Blaster Pro compatible DMA, Extended mode DMA, and programmed I/O. It can be used for either record or playback.

In DOS mode, this channel uses TDMA, DDMA, or PCPCI to emulate ISA DMA on the PCI bus. Since most DOS games default to DMA channel 1, the first audio channel should ideally be assigned to ISA channel 1. However, it is possible to map audio 1 to one of three DMA channels (0,1,3) through the PCI configuration registers.

In Windows mode, this channel can use PCI Bus Master DMA. No ISA resources are required.

Audio 2 The second audio channel. This channel is used for audio playback in full-duplex mode. Audio 2 uses PCI Bus Mastering with burst transfers to minimize PCI bus access.

Figure 5 Data Transfer Modes

# **Data Formats**

See "Data Formats" on page 26.

# Audio 1 DMA Transfers in legacy DOS Compatibility Mode

The first audio channel is programmed using standard commands which support Sound Blaster functionality. These commands are written to the chip through port SBBase+Ch.

When programming the first audio channel for transfers, one of the following modes can be used:

- Direct mode

- DMA modes

- Normal

- Auto-Initialize

In addition, both DMA Normal mode and DMA Auto-Initialize mode can use a special High-Speed mode.

#### **Direct Mode**

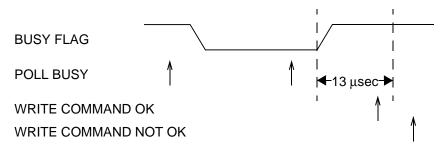

In Direct mode, timing for DMA transfers is handled by the application program. For example, the system timer can be reprogrammed to generate interrupts at the desired sample rate. At each system timer interrupt, the command 10h, 11h, 20h, or 21h is issued followed by the sample. Polling of the Write-Buffer-Available flag (SBBase+Ch [bit 7]) is required before writing the command and between writing the command and the data.

**NOTE:** The switched capacitor filter is initialized by reset for an intended sample rate of 8 kHz. In Direct mode, the application may wish to adjust this filter appropriate to the actual sample rate. Do this by programming the timer with command 40h just as if the application were using DMA mode.

# **DMA Modes**

In DMA mode, the programmable timer in the ES1946 controls the rate at which samples are sent to the CODEC. The timer is programmed using command 40h, which also sets up the programmable filters inside the ES1946. The ES1946 firmware maintains an internal FIFO (32 levels for 16-bit transfers, 64 levels for 8-bit transfers) that is filled by DMA transfers and emptied by timed transfers to the DAC.

Before a DMA transfer, the application first programs the DMA controller for the desired transfer size and address, then programs the ES1946 with the same size information. At the end of the transfer, the ES1946 generates an interrupt request, indicating that the current block transfer is complete. The FIFO gives the application program sufficient time to respond to the interrupt and initiate the next block transfer.

The ES1946 supports both Normal DMA mode and Auto-Initialize DMA mode.

# **Normal DMA Mode**

In Normal mode DMA transfers, the DMA controller must be initialized and the ES1946 commanded for every block that is transferred.

# **Auto-Initialize DMA Mode**

In Auto-Initialize mode, the DMA transfer is continuous, in a circular buffer, and the ES1946 generates an interrupt for the transition between buffer halves. In this mode the DMA controller and ES1946 only need to be set up once.

# **High-Speed Mode**

The ES1946 supports mono 8-bit DMA transfers at a rate up to 44 kHz. Mono 16-bit transfers are supported up to a rate of 22 kHz.

The special "High-Speed mode" allows 8-bit sampling up to 44 kHz for ADC, using commands 98h (auto-initialize) and 99h (normal). No automatic gain control (AGC) is performed. The input volume is controlled with command DDh.

# **Audio 1 DMA Transfers in Extended Mode**

The first audio channel is programmed using the controller registers internal to the ES1946. The commands written to the controller registers are written to the chip through port SBBase+Ch.

When programming the first audio channel for transfers, one of the following modes can be used:

- Programmed I/O

- DMA modes

- Normal (Single or Demand transfer)

- Auto-Initialize (Single or Demand transfer)

In addition, both DMA normal mode and DMA autoinitialize mode use Single transfer or Demand transfer modes.

# Programmed I/O

For some applications, DMA mode is not suitable or available for data transfer, and it is not possible to take exclusive control of the system for DAC and ADC transfers. In these situations, use I/O block transfers within an interrupt handler. The REP OUTSB instruction of the 80x86 family transfers data from memory to an I/O port specified by the DX register. The REP INSB instruction is the complementary function. Use ES1946 port SBBase+Fh for block transfers.

I/O transfers to FIFO are nearly identical to the DMA process, except that an I/O access to port SBBase+Fh replaces the DMA cycle. For details about programmed I/O operation see "Extended Mode Programmed I/O Operation" on page 33.

# **DMA Modes**

Extended mode DMA supports both Normal and Auto-Initialize mode. In addition Normal mode and Auto-Initialize mode both support Single and Demand transfer modes.

# **Single Transfer**

One byte is transferred per DMA request.

# **Demand Transfer**

To reduce the number of DMA requests necessary to make a transfer, two or four bytes are transferred per DMA request (DRQ). Using Demand transfer enables multiple DMA acknowledges for each DMA request.

For a description of DMA mode including Normal DMA mode and Auto-Initialize DMA mode see "DMA Modes" on page 13.

# **Extended Mode Audio 1 Controller Registers**

The following registers control operation of the first audio channel in Extended mode:

Table 2 Extended Mode Audio 1 Controller Registers

| Address | Name                                               |

|---------|----------------------------------------------------|

| A1h     | Audio 1 Sample Rate Generator register             |

| A2h     | Audio 1 Filter Clock Divider register              |

| A4h     | Audio 1 Transfer Count Reload register – low byte  |

| A5h     | Audio 1 Transfer Count Reload register – high byte |

| B1h     | Legacy Audio Interrupt Control register            |

| B2h     | Audio 1 DRQ Control register                       |

| B4h     | Input Volume Control register                      |

| B7h     | Audio 1 Control 1 register                         |

| B8h     | Audio 1 Control 2 register                         |

| B9h     | Audio 1 Transfer Type register                     |

# **Audio 1 DMA Transfers in Native PCI Mode**

Unlike DOS game environments, the ES1946 can be completely controlled by drivers. This way the ES1946 can perform Bus Master DMA for first channel audio data transfers under Windows (or other operating systems).

# **Data Transfers Using the Second Audio Channel**

The second audio channel is programmed using mixer registers 70h through 7Ch. The commands written to the mixer registers are written to the chip through ports SBBase+4h and SBBase+5h.

The second audio channel always uses PCI Bus Master transfers instead of ISA-like DMA. IOBase+0h – IOBase+6h control Audio 2 Bus Master DMA. Both normal and auto-initialize modes are available, as in ISA-DMA. DMA counts for Audio 2 must be in multiples of 16 bytes, so that the ES1946 can performs 4 DWord burst transfers.

**DIGITAL AUDIO**

# **Audio 2 Related Mixer Registers**

The following registers control DMA operations for the second audio channel:

Table 3 Audio 2 Related Mixer Registers

| Address | Name                                               |

|---------|----------------------------------------------------|

| 70h     | Audio 2 Sample Rate register                       |

| 71h     | Audio 2 Mode register                              |

| 72h     | Audio 2 Filter Clock Rate register                 |

| 74h     | Audio 2 Transfer Count Reload register – low byte  |

| 76h     | Audio 2 Transfer Count Reload register – high byte |

| 78h     | Audio 2 Control 1 register                         |

| 7Ah     | Audio 2 Control 2 register                         |

| 7Ch     | Audio 2 DAC Volume Control register                |

# First DMA Channel CODEC

The CODEC of the first audio channel cannot perform stereo DAC and ADC simultaneously. It can either be a stereo DAC or a stereo ADC. After reset, the CODEC is set up for DAC operations. Any ADC command causes a switch to the ADC "direction," and any subsequent DAC command switches the converter back to the DAC "direction."

The DAC output is filtered and sent to the mixer. After reset, input to the mixer from the first audio channel DAC is muted to prevent pops. The ES1946 maintains a status flag to determine if the input to the mixer from the first audio channel DAC is enabled or disabled. Command D8h returns the status of the flag (0h=disabled and FFh=enabled). Use command D1h to enable input to the mixer from the first audio channel DAC and command D3h to disable the input.

To play a new sound without resetting beforehand, when the status of the analog circuits is not clear, mute the input to the mixer with command D3h, then set up DAC direction and level using the direct-to-DAC command:

10h, 80h

Wait 25 milliseconds for the analog circuitry to settle before enabling the voice channel with command D1h.

Pop sounds may still occur if the DAC level was left at a value other than mid-level (code 80h on an 8-bit scale) by the previous play operation. To prevent this, always finish a DAC transfer with a command to set the DAC level to mid-range:

10h, 80h

# **INTERRUPTS**

There are four interrupt sources in the ES1946, shown in Table 4.

Table 4 ES1946 Interrupt Sources

| Interrupt Source | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Audio 1          | An interrupt used for the first DMA channel (Sound Blaster compatible DMA, Extended mode DMA, and Extended mode programmed I/O), as well as MIDI receive that supports Sound Blaster functionality. Controller register B1h controls use of this interrupt for Extended mode DMA and programmed I/O. This interrupt request is cleared by hardware or software reset, or an I/O read from port SBBase+0Eh. The interrupt request can be polled by reading from port SBBase+0Ch or IOBase+07h. |

| Audio 2          | An optional interrupt for the second DMA channel. The ES1946 can operate in full-duplex mode using two DMA channels. The Audio 2 interrupt is masked by bit 6 of mixer register 7Ah. It can be polled and cleared by reading or writing bit 7 of register 7Ah.                                                                                                                                                                                                                                |

| Hardware Volume  | Hardware volume activity interrupt. This interrupt occurs when one of the two hardware volume controls changes state. Bit 1 of mixer register 64h is the mask bit for this interrupt. The interrupt request can be polled by reading bit 3 of register 64h. The interrupt request is cleared by writing any value to register 66h.                                                                                                                                                            |

| MPU-401          | The MPU-401 interrupt occurs when a MIDI byte is received. It goes low when a byte is read from the MIDI FIFO and goes high again quickly if there are additional bytes in the FIFO. The interrupt status is the same as the Read-Data-Available status flag in the MPU-401 status register. The MPU-401 interrupt is masked by bit 6 of mixer register 64h.                                                                                                                                  |

# **Interrupt Status Register**

Port IOBase+7h of the configuration device can be read to quickly find out which ES1946 interrupt sources are active. The bits are:

Table 5 Interrupt Status Bits in IOBase+7h

| Bit | Description                                                               |

|-----|---------------------------------------------------------------------------|

| 4   | Audio 1 interrupt request                                                 |

| 5   | Audio 2 interrupt request AND'ed with bit 6 of mixer register 7Ah         |

| 6   | Hardware volume interrupt request AND'ed with bit 1 of mixer register 64h |

| 7   | MPU-401 receive interrupt request AND'ed with bit 6 of mixer register 64h |

# **Interrupt Mask Register**

Port IOBase+7h can be used to mask any of the four interrupt sources, with the exception of the Audio 1 interrupt. The Audio 1 interrupt request can be enabled by bit 4 of IOBase+7h, or when bit 15 of PCI Configuration register 40h (Legacy Audio Control register) is 0.

The mask bits can be used to force the interrupt source to be zero, without putting the interrupt pin in a high-impedance state. Each bit is AND'ed with the corresponding interrupt source. This register is set to all zeros by hardware reset.

The Interrupt Status register (ISR) is not affected by the state of the Interrupt Mask register (IMR). That is, the ISR reflects the status of the interrupt request lines before being masked by the IMR.

The IMR is useful because the ES1946 shares interrupts. For example, assume that Audio 1, Audio 2, Hardware Volume, and MPU-401 all share the same interrupt in Windows. When returning from Windows to DOS, the Hardware Volume, MPU-401, and Audio 2 interrupts can be masked by setting the appropriate bits to 0.

A second use is within an interrupt handler. The first thing the interrupt handler can do is mask all the interrupt sources mapped to the interrupt handler. Then, the ISR can be polled to decide which sources to process. Just before exiting the interrupt handler, the IMR can be restored. If an unprocessed interrupt remains active, it generates an interrupt request because the interrupt pin was de-asserted during the masked period and then was asserted when the interrupt sources were unmasked. Also, while the interrupts are masked, the individual interrupt sources can change state any number of times without generating a false interrupt request.

# PERIPHERAL INTERFACING

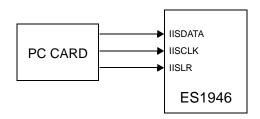

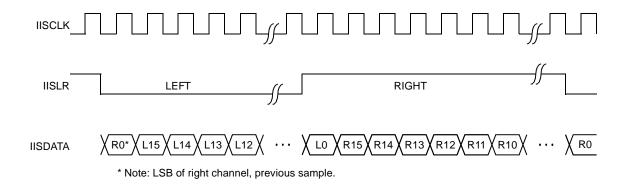

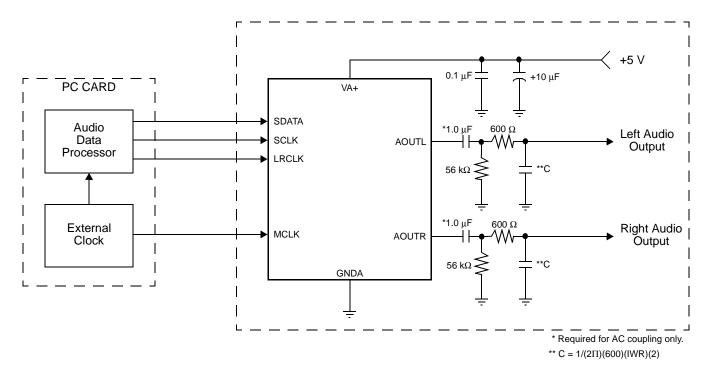

# I'S Serial Interface

Three input pins, IISDATA, IISCLK, and IISLR, are used for a serial interface between an external device and the stereo music DAC within the ES1946. IISDATA, IISCLK, and IISLR can be left floating or connected to ground if the serial interface is not used.

A typical applications of the I<sup>2</sup>S serial interface is MPEG audio or digital CD audio.

Figure 6 I2S Implementation in ES1946

Table 6 I2S Interface Pins

| Pin     | Description                                                                                    |

|---------|------------------------------------------------------------------------------------------------|

| IISDATA | Serial data for I <sup>2</sup> S interface. This pin has an internal pull-down to GNDD.        |

| IISCLK  | Serial shift clock for I <sup>2</sup> S interface. This pin has an internal pull-down to GNDD. |

| IISLR   | Left/Right signal for l <sup>2</sup> S interface. This pin has an internal pull-down to GNDD.  |

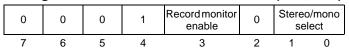

# I<sup>2</sup>S Serial Interface Software Enable

Bit 0 of mixer register 7Fh enables the data bus connection to the I2S interface.

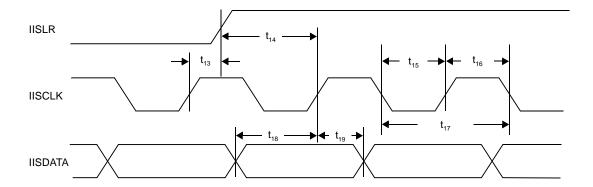

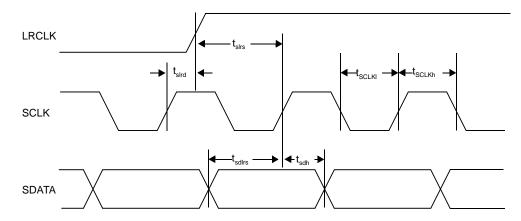

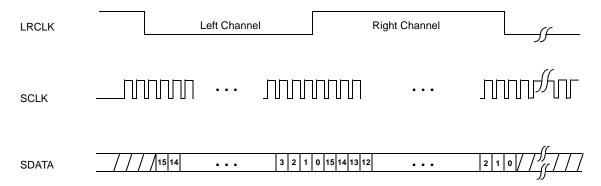

# I'S Serial Interface Timing

This section discusses the I<sup>2</sup>S serial interface signals. The signals when the port is configured for use with an ES689/ES69x wavetable synthesizer are defined in the Wavetable Interface section.

Three signals are used for I2S:

IISCLK The shift clock. The maximum rate is 6.4 MHz. The minimum number of IISCLK periods per IISLR period is 32. Any number greater than or equal to 32 is acceptable.

IISLR Sample synchronization signal. The maximum sample rate is 50 kHz.

IISDATA Serial data.

Within the ES1946, IISLR and IISDATA are sampled on the rising edge of IISCLK. See Figure 18 and Figure 19 for detailed I<sup>2</sup>S timing.

# **Wavetable Interface**

The ES1946 contains a synchronous serial interface for connection to a wavetable music synthesizer.

Table 7 Wavetable Interface Pins

| Pin  | Description                                                                                                                                                                                                                                              |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MCLK | Serial clock from external ES689/ES69x music synthesizer. Input with pull-down.                                                                                                                                                                          |

| MSD  | Serial data from external ES689/ES69x music synthesizer. When both MCLK and MSD are active, the stereo DACs normally used by the FM synthesizer are acquired for use by the external ES689/ES69x. The normal FM output is blocked. Input with pull-down. |

# Joystick / MPU-401 Interface

# MPU-401 UART Mode

There is one MIDI interface in the ES1946, an MPU-401 "UART mode" compatible serial port. MPU-401 is a superior method of MIDI serial I/O because it does not interfere with DAC or ADC Sound Blaster commands.

MPU-401 requires an interrupt channel for MIDI receive. This interrupt should be selected using mixer register 64h. It should be different than the interrupt selected for audio DMA interrupts.

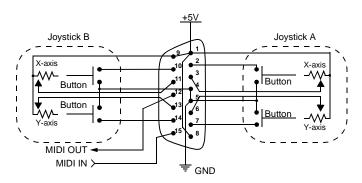

# Joystick / MIDI External Interface

The joystick portion of the ES1946 reference design is identical to that on a standard PC game control adaptor or game port. The PC compatible joystick can be connected to a 15-pin D-sub connector. It supports all standard PC joystick-compatible software. If the system already has a game card or port, remove the game card.

If multiple joysticks are required, use a joystick conversion cable. This cable uses a 15-pin D-sub male connector on one end, and two 15-pin D-sub female connectors on the other end. All signals on this cable have direct pin-to-pin connection, except for pins 12 and 15. On the male

connector, pins 12 and 15 should be left without connection. On the female connectors, pin 15 is internally connected to pin 8, and pin 12 is internally connected to pin 4. The dual joystick and MIDI port take up only one slot in the system, leaving room for other cards. Figure 7 shows the dual joystick/MIDI connector configuration.

Figure 7 Dual Joystick/MIDI Connector

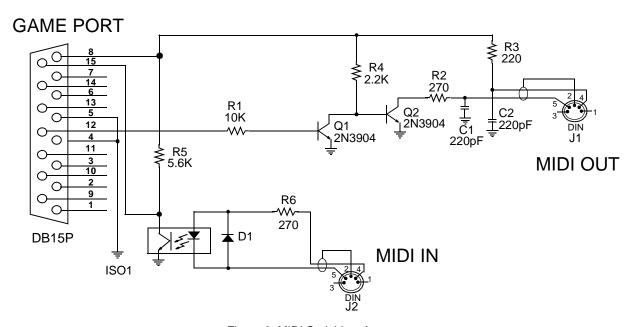

Figure 8 shows the MIDI serial interface adaptor from the joystick/MIDI connector.

Figure 8 MIDI Serial Interface

# MONO\_IN and MONO\_OUT

MONO\_IN is a line-level analog input. MONO\_IN is an input to the playback mixer and the record mixer. The mixer volumes are controlled by mixer registers 6Dh (playback) and 6Fh (record).

Alternately, MONO\_IN can be mixed with AOUT\_L and AOUT\_R after the master volume stage. Bit 0 of mixer register 7Dh, when high, enables MONO\_IN to be mixed directly (unity gain) with AOUT\_L and AOUT\_R.

MONO\_OUT is a line-level mono output. During power-down or during opamp calibration, MONO\_OUT is held at CMR (as are AOUT\_L and AOUT\_R) by an internal, high-impedance resistor divider. MONO\_OUT can be selected from among four sources by bits 2 and 1 of mixer register 7Dh.

| Mixer Register 7Dh |       | MONO_OUT Source                                  |  |

|--------------------|-------|--------------------------------------------------|--|

| Bit 2              | Bit 1 | WONO_OOT Source                                  |  |

| 0                  | 0     | Mute (CMR)                                       |  |

| 0                  | 1     | First channel filter output (actually CIN_R pin) |  |

| 1                  | 0     | Second channel DAC, right channel                |  |

| 1                  | 1     | Mono mix of record level stage outputs           |  |

Normally bits 2:1 are both zero, so that MONO\_OUT is muted.

When bit 2 is 0 and bit 1 is 1, MONO\_OUT is a buffered version of input pin CIN\_R. CIN\_R is typically the right channel DAC output, filtered by the first channel switched-capacitor filter. If the right channel is used for ADC, CIN\_R will be the right channel ADC input. MONO\_OUT can be used in this application as digitized audio playback through the first channel DMA, right channel DAC.

When bit 2 is 1 and bit 1 is 0, MONO\_OUT is a buffered version of the second channel, right channel DAC. In this case, the second channel DMA can play digitized audio through MONO\_OUT.

When bit 2 is 1 and bit 1 is 1, MONO\_OUT is a buffered version of a mono mix of the record level stage left and right outputs. This gives the utmost flexibility in the source or sources of MONO\_OUT. The record source select and record levels can be programmed to generate any combination of sources and volumes for MONO\_OUT.

# **Spatializer® VBX™ Audio Processor**

The ES1946 incorporates an embedded **Spatializer** VBX<sup>™</sup> stereo audio processor provided by Desper Products, Inc., a subsidiary of Spatializer Audio Laboratories, Inc. It is positioned between the output of the playback mixer and the master volume controls and it produces a wider perceived stereo effect.

The 3-D effect is enabled by register 50h bit 3. The amount of effect is controlled by directly programming 3-D Effect Level register 52h.

# **Hardware and Master Volume Control**

Two external pins, VOLUP and VOLDN, can be connected to external momentary switches to ground to implement hardware master volume controls. Pressing one of these buttons produces a low signal to one of the inputs and thereby changes the master volume.

MUTE is emulated by the state where both VOLUP and VOLDN inputs are low simultaneously.

The up and down buttons produce a single step change in volume when they are first pressed. If these buttons are held down, they enter a fast-scrolling mode. The single step change can be either one volume unit (.75 dB) or three volume units (2.25 dB). In scrolling mode, the step change is always one volume unit.

The two inputs have debounce circuitry within the ES1946. Hold each input low for 40 milliseconds or more for it to be recognized as a valid button press. Hold each input high for 40 milliseconds or more between button presses. A software option allows the debounce time to be reduced from 40 milliseconds to 10 microseconds.

Normally the hardware volume controls directly change the master volume registers and produce an interrupt at each change. However, the ES1946 can be programmed so that the hardware volume controls do not directly change the master volume registers. This is called "split mode", in which the hardware volume control counters are split from the master volume registers. Pressing a hardware volume control button changes the hardware volume counters and produces an interrupt. The host software can read the hardware volume counters and update the master volume registers as needed. Split mode is enabled by bit 7 of mixer register 64h.

For support of mixer master volume control, a write to mixer registers 22h or 32h translates automatically into writes to the master volume registers. Since register 22h only has 3-bit resolution per channel, and register 32h only has 4-bit resolution per channel, a translation circuit is included in the ES1946 that translates 3- or 4-bit volume

values into the 6-bit volume + mute that is used in the master volume registers. Support of these mixer registers can be defeated under software control.

Reading master volume registers 22h or 32h also requires a translation circuit to translate 6-bit + mute master volumes into 3- or 4-bit master volume numbers for registers 22h or 32h.

# **PC Speaker**

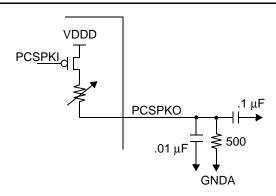

20

The PC Speaker is supported with a 1-bit DAC with volume control. The analog output pin PCSPKO is intended to be externally mixed at the external amplifier.

# **PC Speaker Volume Control**

When the PCSPKI signal is high, a resistive path to analog power is enabled. The value of the resistor is selected from among 7 choices to control the amplitude of the output signal.

Figure 9 PC Speaker Volume Circuitry

With the external circuit shown in Figure 9, the amplitude of a square wave output on pin PCSPKO should be approximately VDDD/2 for maximum volume, i.e., the internal resistor is approximately 500 ohms ( $\pm$  30%). The other levels are relative to this amplitude as follows:

mute, -24dB, -21dB, -18dB, -15dB, -12dB, -9dB, -6dB

The purpose of the circuit, beyond volume control of the speaker, is to prevent digital noise from the PC speaker signal being mixed into the analog signal. This circuit provides a clean analog signal. The output can be either mixed with the AOUT\_L and AOUT\_R pins externally or it can be used to drive a simple transistor amplifier to drive an 8 ohm speaker dedicated to producing beeps.

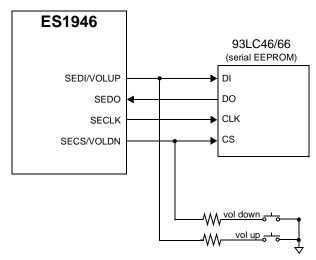

# Serial EEPROM Interface

The ES1946 gets Subsystem ID (SID) and Subsystem Vendor ID (SVID) from an external EEPROM device. The external EEPROM is accessed by the ES1946 immediately after the PRSTB pin becomes inactive. The ES1946 supports 93LC46 and 93LC66 serial EEPROMs.

The EEPROM interface is shared with the hardware volume controls. When the EEPROM interface is active, the volume controls are deactivated. See Figure 10.

#### **EEPROM ROM FORMAT**

The first byte should be the EEPROM identifier

| Device | 1st Byte |

|--------|----------|

| 93LC46 | 46h      |

| 93LC66 | 66h      |

The second byte is the signature byte for the ES1941 and ES1946. The signature byte must be 38h.

# **Example EEPROM Code**

Figure 10 Serial EEPROM - Typical Application

PERIPHERAL INTERFACING

# Programming the EEPROM

After reset, the ES1946 reads six bytes from the EEPROM. The ES1946 can read, write, or erase all the bits stored in the EEPROM. The ES1946 accesses the EEPROM by means of three I/O ports.

```

IOBase+2Dh Device Select

IOBase+2Eh EEPROM Data

IOBase+2Fh EEPROM Command

```

# **EEPROM Access Example**

```

/* This example illustrates usage of EEPROM i/f */

#define READ

0x8

#define EWEN

0x3

#define EWDS 0x0

#define WRITE 0x4

#define WRAL 0x1

#define ERASE 0xc

#define ERAL 0x2

/* select device type. must be called before

other routine is called, if EEPROM didn't

contain right Device Identifier (first byte)

at boot time. */

void select_eeprom (int dev)

switch (dev) {

case 0x46:

outp (iobase+0x2d, 0x01);

break;

default:

outp (iobase+0x2d, 0x03);

break;

pause (2);

/* n bytes write to EEPROM */

void eepromWrite (int eeaddr, int *eedata, int n)

{

int i;

unsigned int index;

char line[10];

outp (iobase+0x2f, EWEN); //enable erase/write

pause (1);

gotoAddr (eeaddr);

for (i=0; i<n; i++) {

outp (iobase+0x2e, *eedata++);

outp (iobase+0x2f, WRITE);

pause (10);// wait 10 msec

}

outp (iobase+0x2f, EWDS); //disable erase/write

}

```

```

/* n bytes read from EEPROM */

void eepromRead (int eeaddr, int *eedata, int n)

int i;

int *p;

gotoAddr(eeaddr);

for (i=0, p=eedata; i<n; i++) {

outp(iobase+0x2f, READ);

pause (1);

*p++ = inp (iobase+0x2e);

pause (1);

}

/* erase all data */

void eepromEraseAll(void)

{

int i;

outp(iobase+0x2f, EWEN); //enable erase/write

pause(1);

outp(iobase+0x2f, ERAL);

pause(15); //wait 15 msec

outp(iobase+0x2f, EWDS); //disable erase/write

void gotoAddr (int addr)

{

int i;

inp (iobase+0x2f); //reset eeprom address

pause (1);

for (i=0; i<addr; i++) {

outp (iobase+0x2f, READ);

pause (1);

(void) inp (iobase+0x2e);

pause (1);

}

```

# ANALOG DESIGN CONSIDERATIONS

This section describes design considerations related to inputs and outputs of analog signals and related pins on the chip.

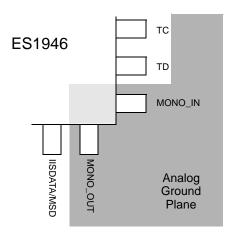

# MONO IN and MONO OUT

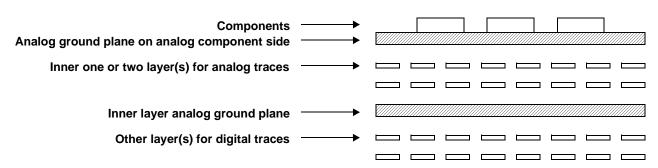

MONO\_IN and MONO\_OUT are bound by digital signals on either side. When laying out a PCB, MONO\_IN and MONO\_OUT must be in the analog ground plane and well isolated from the digital ground plane.

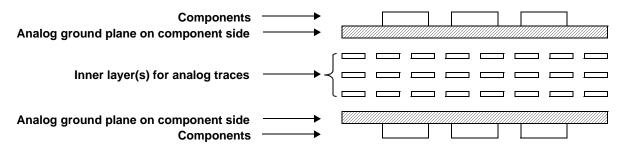

Figure 11 Analog Ground Plane Diagram

# **Reference Generator**

Reference generator pin CMR is shown bypassed to analog ground.

Figure 12 Reference Generator Pin Diagram

# **Switched-Capacitor Filter**

The outputs of the FOUT\_L and FOUT\_R filters must be AC-coupled to the inputs CIN\_L and CIN\_R. This provides for DC blocking and an opportunity for low-pass filtering with capacitors to analog ground at these inputs.

Figure 13 Switched-Capacitor Filter Pin Diagram

# **Audio Inputs and Outputs**

Analog inputs MIC, MONO\_IN, LINE\_L, LINE\_R, AUXA\_L, AUXA\_R, AUXB\_L, and AUXB\_R should be capacitively coupled to their respective input signals. All have pull-up resistors to CMR.

ES1946 analog outputs MONO\_OUT, AOUT\_L and, AOUT\_R should be AC-coupled to an amplifier, volume control potentiometer, or line-level outputs.

# PROGRAMMING THE ES1946

# Identifying the ES1946

The ES1946 device can be identified using the PCI standard configuration register. Offset 00h contains the registered Vendor ID (VID), which for ESS is 125Dh. Offset 02h contains the assigned Device ID (DID), which for the ES1946 is 1969h.

In addition, the ES1946 has a Subsystem Vendor ID (SVID) and Subsystem ID (SID). These two registers default values are read from the EEPROM immediately after PRSTB becomes inactive. If the EEPROM signature check fails (if no EEPROM is connected, for example), the default values become 125Dh and 8888h respectively. If the ES1946 is mounted on the motherboard, the system BIOS can program these two registers so that the EEPROM is not needed.

# Resetting and Initializing the ES1946

The ES1946 chip can be reset in one of two ways: hardware or software reset.

The hardware reset signal comes from the PCI bus and it initializes:

- · PCI configuration registers

- · the microcontroller

- · internal FIFOs

- · the ESFM synthesizer

- · the mixer registers

- · the analog mixer

- CODECs

The software reset is controlled by bit 0 of port SBBase+6h and it initializes:

- · the microcontroller

- · the ESFM synthesizer

- · the analog mixer

- the CODEC

To reset the ES1946 by software:

- 1. Set bit 0 of SBBase+6h.

- 2. Delay a short period by reading back SBBase+6h.

- 3. Clear bit 0 of SBBase+6h.

- In a loop lasting at least 1 millisecond, poll port SBBase+Eh bit 7 for Read Data Available. Exit the loop only if bit 7 is high and SBBase+Ah returns 0AAh.

Table 8 Hardware and Software Reset Initializations

| Initialization                                           | Hardware<br>Reset | Software<br>Reset |

|----------------------------------------------------------|-------------------|-------------------|

| Disable Extended Mode                                    | Yes               | Yes               |

| Reset the timer divider and filter for 8 kHz             | Yes               | Yes               |

| Stop any DMA transactions in progress                    | Yes               | Yes               |

| Clear any active interrupt requests                      | Yes               | Yes               |

| Disable voice input of mixer                             | Yes               | Yes               |

| Compatibility/Extended mode DMA counters to 2048 bytes   | Yes               | Yes               |

| Set audio 1 CODEC direction to DAC                       | Yes               | Yes               |

| Set DAC volumes to mid-level                             | Yes               | Yes               |

| Set input volume for 8-bit recording with AGC to maximum | Yes               | Yes               |

| All other mixer registers to default values              | Yes               | No                |

| Internal FIFO in extended mode                           | Yes               | No¹               |

| PCI Configuration registers                              | Yes               | No                |

<sup>1.</sup> Bit 1 of SBBase+6h can reset internal FIFOs.

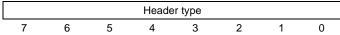

After the system powers up, the PCI BIOS initializes the header portion (00h–3Fh) of the PCI configuration space. The PCI BIOS can also program the SID and SVID registers.

After the PCI BIOS initializes the device, the ES1946 is in Native mode. All of the PCI configuration registers should be set up properly before the ES1946 accesses any other registers.

# **Programming for DOS Game Compatibility**

The ES1946 is fully compatible to legacy DOS games with Sound Blaster Pro functionality. To achieve high compatibility to a legacy ISA device on the PCI bus, two major issues need to be addressed. The first issue concerns ISA DMA and the second issue concerns ISA IRQ.

# **ISA DMA**

To emulate ISA DMA on the PCI bus, the ES1946 can employ three different protocols:

TDMA Transparent DMA, a chipset

independent mechanism

DDMA Distributed DMA, must be supported

by the PCI chipset

PC/PCI DMA PC to PCI DMA, must be supported by

the PCI chipset

Once one of the three DMA protocols is set up, the ES1946 is seen as an ISA device.

#### **TDMA**

In TDMA, the ES1946 snoops PCI bus transactions to a legacy DMA controller device then performs a PCI bus master transaction to complete DMA.

#### **DDMA**

In DDMA, the central resource (PCI chipset) includes a DMA remap engine. All transactions to legacy DMACs are remapped to each client (such as the ES1946) by the remap engine. The ES1946 then performs a PCI bus master transaction.

# PC/PCI DMA

In PC/PCI DMA, the central resource (PCI chipset) performs PC/PCI cycles, which use sideband signals to the standard PCI bus. The ES1946 then acts as a slave device during DMA.

# **ISA IRQ**

The second issue concerns ISA IRQ. The ISA IRQ is edge triggered while PCI IRQ is level sensitive. By configuring the IRQ policy bits in PCI Configuration register 50h, the ES1946 can emulate ISA IRQ.

Setting bit 15 of Legacy Audio Control register (LACR, PCI Configuration register 40h) to 0, allows the ES1946 to decode legacy audio addresses.

# Selecting DMA/IRQ Policy

Because PCI chipsets do not all support the same DMA protocols, DMA policy should be selected according to the chipset in use. Table 9 and Table 10 list the recommended DMA policies for Intel chipsets for add-on cards and motherboards respectively. To find out which DMA policy

to use with non-Intel chipset, contact your ESS FAE. DMA policy is configured in PCI Configuration register 50h, bits [10:8].

Table 9 ISA DMA Policy Bits for Add-On Cards

| Chipset                | Protocol | DMA Policy |       |       |  |

|------------------------|----------|------------|-------|-------|--|

| Chipset                | FIOLOCOI | Bit 10     | Bit 9 | Bit 8 |  |

| Intel 430FX (Triton)   | TDMA     | 0          | 0     | 1     |  |

| Intel 430HX (Triton-2) | TDMA     | 0          | 0     | 1     |  |

| Intel 430VX (Triton-3) | TDMA     | 0          | 0     | 1     |  |

| Intel 430TX            | DDMA     | 0          | 0     | 0     |  |

| Intel 440LX            | TDMA     | 1          | 0     | 0     |  |

| Intel 440BX/EX         | DDMA     | 0          | 0     | 0     |  |

| IIILEI 440DA/EA        | TDMA     | 1          | 0     | 0     |  |

Table 10 ISA DMA Policy Bits for Motherboards

| Chinaat                | Protocol | DMA Policy |       |       |  |

|------------------------|----------|------------|-------|-------|--|

| Chipset                | Protocol | Bit 10     | Bit 9 | Bit 8 |  |

| Intel 430FX (Triton)   | TDMA     | 0          | 0     | 1     |  |

| Intel 430HX (Triton-2) | TDMA     | 0          | 0     | 1     |  |

| Intel 430VX (Triton-3) | TDMA     | 0          | 0     | 1     |  |

| Intel 430TX            | DDMA     | 0          | 0     | 0     |  |

| Intel 440LX            | PCPCI    | 0          | 1     | 0     |  |

| IIII.EI 440LX          | TDMA     | 1          | 0     | 0     |  |

|                        | PCPCI    | 0          | 1     | 0     |  |

| Intel 440BX/EX         | DDMA     | 0          | 0     | 0     |  |

|                        | TDMA     | 1          | 0     | 0     |  |

To emulate ISA IRQ on the PCI bus, program the IRQ emulation policy bits, unless SERIRQ is used. Table 11 lists the program IRQ Policy bits. Program the policy bits according to the IRQ level selected for the ES1946's INTAB pin. IRQ policy is configured in PCI Configuration register 50h, bits [14:13].

Table 11 ISA IRQ Emulation Policy Bits

| PCI IRQ (INTAB Pin)          | IRQ Policy |        |  |

|------------------------------|------------|--------|--|

| reing (INIAB FIII)           | Bit 14     | Bit 13 |  |

| IRQ 5/7/9/10                 | 0          | 1      |  |

| IRQs other than IRQ 5/7/9/10 | 1          | 0      |  |

PCI Configuration register 3Ch is set by the PCI BIOS, and it indicates which IRQ the ES1946 INTAB pin is using. PCI Configuration register 40h (Legacy Audio Control register), bits[9:8] indicate which IRQ is used by the DOS game.

PROGRAMMING THE ES1946

# **Programming for Native PCI Audio**

When the ES1946 is configured as a native PCI device, the audio channels must be configured properly, as shown in the procedures below. The ES1946 is a bus master device.

# **Configuring Audio 1 in Native Mode**

- Set up the DDMA Control register.

The PCI BIOS reserves I/O regions (16 bytes), and stores them in the VCBase register. Copy the VCBase register (PCI Configuration register 18h) to the DDMA Control register (PCI Configuration register 60h), with bit 0 set.

- Select the DMA/IRQ policy.

The DMA policy should be set for DDMA (PCI Configuration register 50h, bits 10:8 = 000). The ISA IRQ emulation should be disabled (PCI Configuration register 50h, bits 14:13 = 00).

- Program the legacy DOS compatible module.

See "Extended Mode Audio 1 DAC Operation" on page 30.

- 4. Program the DMA controller. Instead of using 8237 (DMAC), the program should use the built-in DMAC inside the ES1946. The built-in DMAC is accessed as I/O address range DDMABase+0h to DDMABase+Fh. Use the following sequence to program the built-in DMAC.

- Master reset.

Write any data to DDMABase+Dh.

- 2. Mask DMA.

Write 1 to DDMABase+Fh.

- 3. Set up DMA mode.

Write the mode value to DDMA Base+Bh.

- Setup DMA base address and counts.

Write the base address to DDMABase+0h.

Write the base count to DDMABase+4h.

- 5. Unmask DMA.

Write 0 to DDMABase+Fh.

# **Configuring Audio 2 in Native Mode**

Unlike programming for Audio 1 in native mode, all I/O spaces are allocated by PCI BIOS.

- Program the legacy ESS AudioDrive® controller module. See "Second Audio Channel DAC Operation" on page 33.

- Program the DMA controller.

Instead of using 8237 (DMAC), the program should use the built-in DMAC inside the ES1946. The built-in DMAC is accessed as I/O address range IOBase+0h to IOBase+6h. Use the following sequence to program the built-in DMAC.

- Disable DMA.

Clear bit 1 of IOBase+6h. Preserve all other bits.

- Set up DMA mode. Program bit 3 of IOBase+6h. Preserve all other bits

- Set up DMA base address and counts.

Write the base address to IOBase+0h.

Write the base count to IOBase+4h.

- 4. Enable DMA.

Set bit 1 of IOBase+6h. Preserve all other bits.

# **Modes of Operation**

The ES1946 can operate the first audio channel in one of two modes: Compatibility mode or Extended mode.

In both modes, a set of mixer and controller registers enables application software to control the analog mixer, record source, and output volume. Programming the ES1946 Enhanced Mixer is described later in this document. See "Programming the ES1946 Mixer" on page 35.

# **Compatibility Mode Description**

The first mode, Compatibility mode, is compatible to legacy DOS. This is the default mode after reset. In this mode, the ES1946 microcontroller is an intermediary in all functions between the PCI bus and the CODEC. The ES1946 microcontroller performs limited FIFO functions using 64 bytes of internal memory.

# **Extended Mode Description**

The ES1946 also supports an Extended mode of operation. In this case, a 256-byte FIFO is used as an intermediary between the PCI bus and the ADC and DAC Control registers, and various Extended mode controller registers are used for control. The ES1946 microcontroller is mostly idle in this mode. DMA control is handled by dedicated logic. Programming for Extended mode operation requires accessing various control registers with ES1946 commands.

Table 12 Comparison of Operation Modes

|                                               | Compatibility Mode<br>(Legacy DOS)        | Extended Mode                |

|-----------------------------------------------|-------------------------------------------|------------------------------|

| Legacy DOS compatible                         | Yes                                       | No                           |

| FIFO Size                                     | 64 bytes (firmware managed)               | 256 bytes (hardware managed) |

| Mono 8-bit ADC, DAC                           | Yes, to 44 kHz                            | Yes, to 48 kHz               |

| Mono 16-bit ADC, DAC                          | Yes, to 22 kHz                            | Yes, to 48 kHz               |

| Stereo 8-bit DAC                              | Yes, to 22 kHz                            | Yes, to 48 kHz               |

| Stereo 8-bit ADC                              | Yes, to 22 kHz                            | Yes, to 48 kHz               |

| Stereo 16-bit DAC                             | Yes, to 11 kHz                            | Yes, to 48 kHz               |

| Stereo 16-bit ADC                             | No                                        | Yes, to 48 kHz               |

| Signed/Unsigned Control                       | No                                        | Yes                          |

| Automatic Gain Control during recording       | Firmware controlled, to 22 kHz, mono only | No                           |

| Programmed I/O block transfer for ADC and DAC | No                                        | Yes                          |

| FIFO status flags                             | No                                        | Yes                          |

| Auto reload DMA                               | Yes                                       | Yes                          |